Clock and Data Recovery/Structures and types of CDRs/The CDR phase comparator - Wikibooks, open books for an open world

Figure 2 from A Half-Rate Bang-Bang Phase/Frequency Detector for Continuous-Rate CDR Circuits | Semantic Scholar

Clock and Data Recovery/Structures and types of CDRs/The CDR Phase and Frequency Detector PFD - Wikibooks, open books for an open world

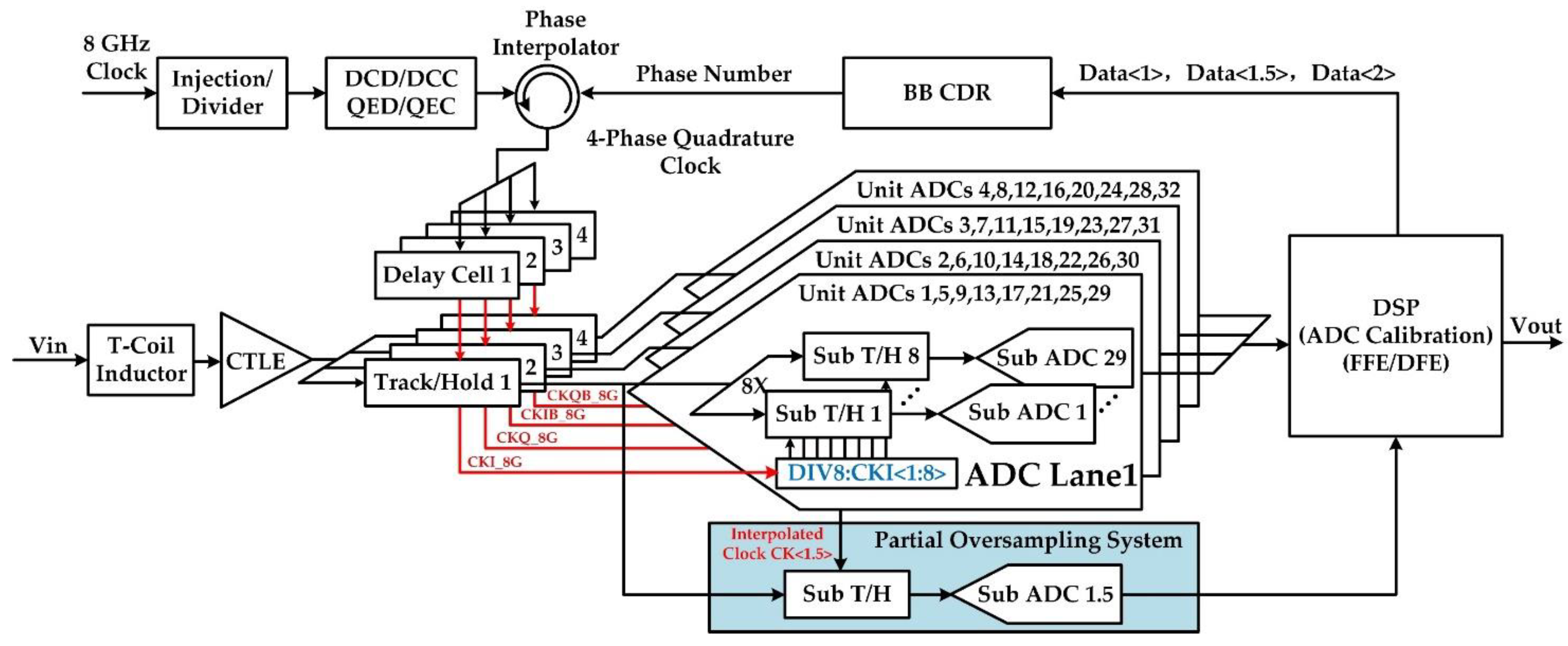

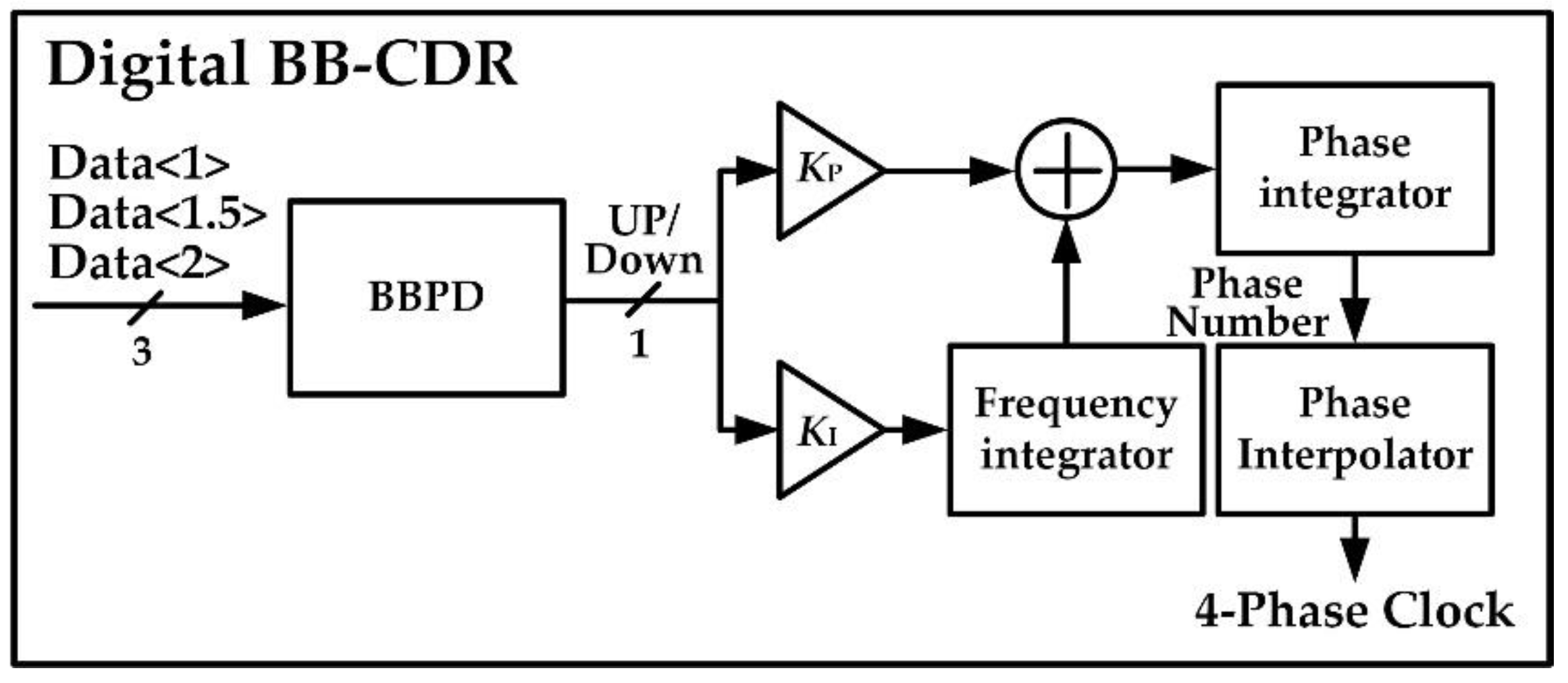

Electronics | Free Full-Text | A Digital Bang-Bang Clock and Data Recovery Circuit Combined with ADC-Based Wireline Receiver